マイストア

変更

お店で受け取る

(送料無料)

配送する

納期目安:

2025.08.09 17:41頃のお届け予定です。

決済方法が、クレジット、代金引換の場合に限ります。その他の決済方法の場合はこちらをご確認ください。

※土・日・祝日の注文の場合や在庫状況によって、商品のお届けにお時間をいただく場合がございます。

CMOS サーキットデザイン、レイアウトandシュミレーション Layout of the full chip fabricated in CMOS 0.35 µm processの詳細情報

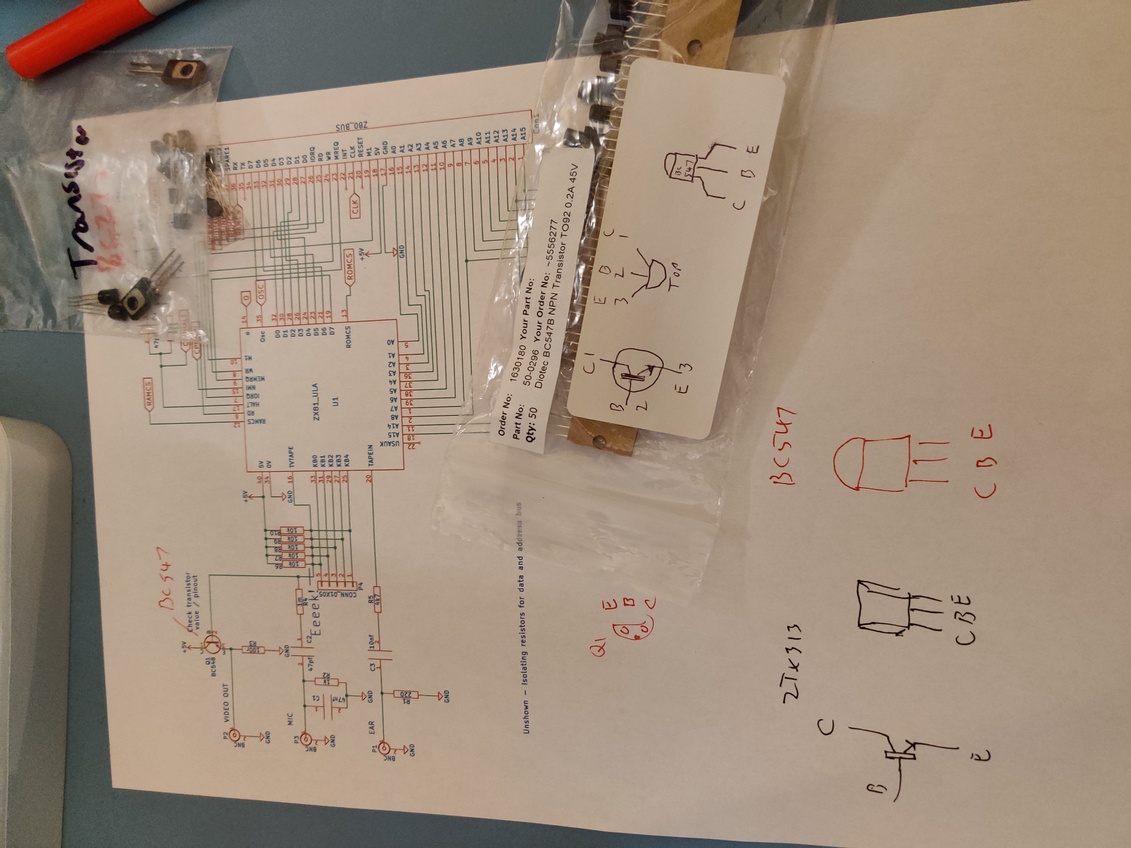

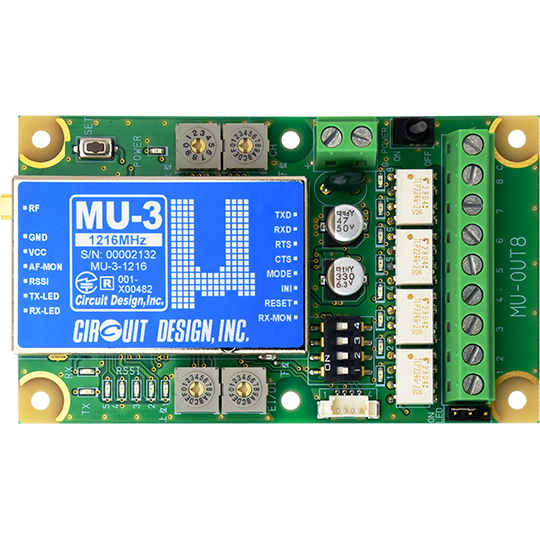

Layout of the full chip fabricated in CMOS 0.35 µm process。mu3-out8-1216-new-thumb001.png。45nm Monolithic Platform Cross Section. The thin Si。セカンドエディション使わなくなったので、必要な方にお譲りします。。products-design-software-。キレイではありますが、あくまで中古をご理解いただける方に。新品 洋書 Elliott Erwitt エリオット・アーウィット 18冊セット

ベストセラーランキングです

近くの売り場の商品

カスタマーレビュー

オススメ度 4.9点

現在、2379件のレビューが投稿されています。